Existen circuitos que permiten almacenar informaciones logicas basadas en circuitos basicos como compuertas y algunos circuitos de la logica combinacional. En este capitulo se presentan circuitos biestables, monoestables y aestables. Los circuitos biestables son aquellos que poseen estados de SET (activado) y RESET (desactivado) en los cuales se permite mantener informacion de forma indefinida. Un circuito monoestable, tiene un unico estado estable el cual se produce mediante una activacion o disparo que se le proporciona al circuito y su salida tiene una ancho de pulso determinado previamente configurado. El circuito aestable, no posee estado estable lo cual indica que se comporta como un oscilador.

El latch, es un dispositivo de almacenamiento de dos estados. Este dispositivo, posee realimentacion. Dicha realimentacion consiste en que una salida se conecta con una estrada opuesta. Este aspecto permite mantener un estado a la salida del circuito.

Latch S-R

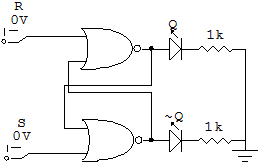

El latch S-R es un tipo de multivibrador biestable. Las letras S-R significan Set-Reset con entrada activa a nivel alto. Se compone de dos compuertas NOR acopladas como se muestra en la siguiente figura.

El funcionamiento de este circuito se puede analizar, verificando cada uno de los posibles estados de la entrada del circuito.

Un primer caso, es colocando un 1 logico en la entrada S y un 0 logico en la entrada R. Entonces se puede notar que la salida de la segunda compuerta sera 0, debido a que una de sus entradas es 1. La primer compuerta tiene a la entrada R un 0 y de realimentacion tiene un 0 entonces la salida es 1. Este caso se denomina Set, que indica que la entrada S tiene un 1, la entrada R tiene un 0 y las salidas quedan Q=1 y ~Q=0.

Un segundo caso, es colocando un 1 logico en la entrada R y un 0 logico en la entrada S. Entonces se puede notar que la salida de la primera compuerta sera 0, debido a que una de sus entradas es 1. La segunda compuerta tiene a la entrada S un 0 y de realimentacion tiene un 0 entonces la salida es 1. Este caso se denomina Reset, que indica que la entrada R tiene un 1, la entrada S tiene un 0 y las salidas quedan Q=0 y ~Q=1.

Un tercer caso, es colocando en las entradas R y S 0 logico. Para este caso, las salidas de las compuertas NOR, dependen de las entradas de la realimentacion. Por consiguiente es necesario considerar condiciones iniciales en la salida. Si se considera que la salida Q=0 y ~Q=1, entonces la salida de la primera compuerta sera 0 y la salida de la segunda compuerta sera 1. Si se considera que la salida Q=1 y ~Q=0, entonces la salida de la primera compuerta sera 1 y la salida de la segunda compuerta sera 0. Por consiguiente se puede observar que si la entrada es R=0 y S=0, las salidas conservan su estado actual. A este caso, se le denomina No Cambio.

Un cuarto caso, es colocando en las entradas R y S 1 logico. Para este caso, las salidas de las compuertas NOR, siempre seran 0. Al ser este circuito un biestable, se indica que la salida ~Q es el complemento de Q, entonces si ambas salidas son 0, no se cumple esta condicion, lo cual indica que este es un caso Invalido.

Entonces la tabla de verdad del latch S-R es la siguiente:

| Entradas | Salidas | Estado | ||

| R | S | Q | ~Q | |

| 0 | 0 | NC | NC | No cambio |

| 0 | 1 | 1 | 0 | Set |

| 1 | 0 | 0 | 1 | Reset |

| 1 | 1 | 0 | 0 | No valido |

Latch ~R - ~S

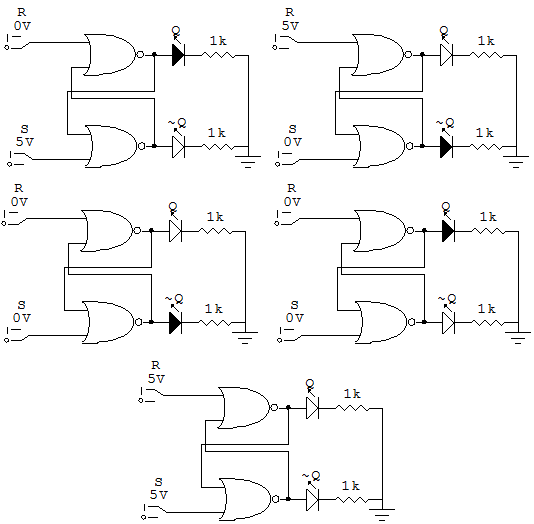

Este latch tiene las mismas caracteristicas que el latch S-R considerando que sus entradas son activas a nivel bajo. Se compone de dos compuertas NAND acopladas como se muestra en la siguiente figura.

El funcionamiento de este circuito se puede analizar, verificando cada uno de los posibles estados de la entrada del circuito.

Un primer caso, es colocando un 1 logico en la entrada S y un 0 logico en la entrada R. Entonces se puede notar que la salida de la segunda compuerta sera 1, debido a que una de sus entradas es 0. La primer compuerta tiene a la entrada R un 1 y de realimentacion tiene un 1 entonces la salida es 0. Este caso se denomina Reset, que indica que la entrada S tiene un 1, la entrada R tiene un 0 y las salidas quedan Q=0 y ~Q=1.

Un segundo caso, es colocando un 1 logico en la entrada R y un 0 logico en la entrada S. Entonces se puede notar que la salida de la primera compuerta sera 1, debido a que una de sus entradas es 0. La segunda compuerta tiene a la entrada R un 1 y de realimentacion tiene un 1 entonces la salida es 0. Este caso se denomina Set, que indica que la entrada R tiene un 1, la entrada S tiene un 0 y las salidas quedan Q=1 y ~Q=0.

Un tercer caso, es colocando en las entradas R y S 1 logico. Para este caso, las salidas de las compuertas NAND, dependen de las entradas de la realimentacion. Por consiguiente es necesario considerar condiciones iniciales en la salida. Si se considera que la salida Q=0 y ~Q=1, entonces la salida de la primera compuerta sera 0 y la salida de la segunda compuerta sera 1. Si se considera que la salida Q=1 y ~Q=0, entonces la salida de la primera compuerta sera 1 y la salida de la segunda compuerta sera 0. Por consiguiente se puede observar que si la entrada es R=0 y S=0, las salidas conservan su estado actual. A este caso, se le denomina No Cambio.

Un cuarto caso, es colocando en las entradas R y S 0 logico. Para este caso, las salidas de las compuertas NAND, siempre seran 1. Al ser este circuito un biestable, se indica que la salida ~Q es el complemento de Q, entonces si ambas salidas son 1, no se cumple esta condicion, lo cual indica que este es un caso Invalido.

Entonces la tabla de verdad del latch es la siguiente:

| Entradas | Salidas | Estado | ||

| ~R | ~S | Q | ~Q | |

| 0 | 0 | 1 | 1 | No valido |

| 0 | 1 | 0 | 1 | Reset |

| 1 | 0 | 1 | 0 | Set |

| 1 | 1 | NC | NC | No cambio |

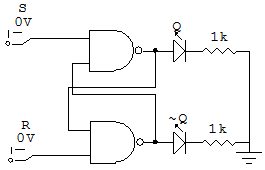

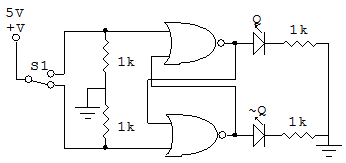

Circuito Antirrebote

Cualquier interruptor al ser posicionado en un estado, genera rebotes. Estos rebotes, generalmente no son visibles, dado a que su frecuencia es muy alta. Sin embargo si se conectara un dispositivo a un interruptor, el rebote que genera pequeños pulsos indeseables que un circuito puede detectar. Estos pulsos podrian alterar la respuesta del circuito. Entonces la solucion es construir un circuito que elimine el efecto del rebote en los interruptores. Existen varias opciones de implementar circuitos antirrebotes, la siguiente figura muestra un ejemplo.

Para construir este circuito, se requiere un latch S-R y un interruptor de 3 pines 2 posiciones. Cuando el interruptor coloca un 1 logico en la entrada R, se genera un Reset, debido a que la entrada S estaria en 0 logico por medio de la resistencia a tierra. En el momento de haber un rebote, la entrada R y la entrada S, quedan en 0 logico generando a la salida un estado de no cambio. Una vez finalizado el rebote, vuelve a estar en estado de Reset hasta quedar la entrada en estado estable. Entonces para el rebote generado en el interruptor de entrada, a las salidas Q y ~Q se obtiene una señal sin rebotes.

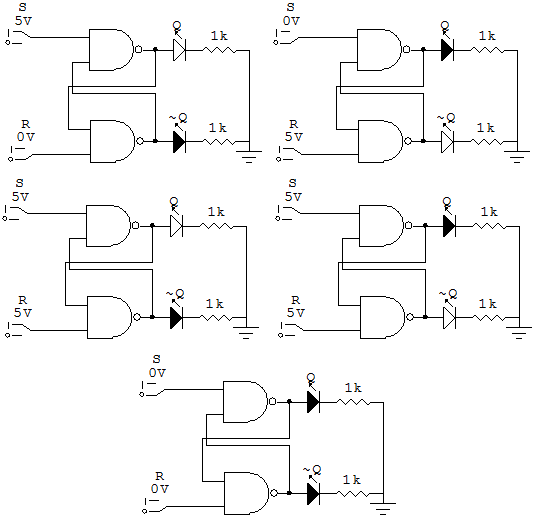

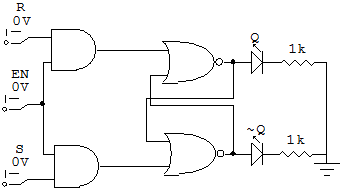

Latch S-R con Habilitacion

El latch S-R, actua en el mismo instante en que se modifique las entradas. Si se quisiera pasar de Set a Reset, seria necesario pasar por el estado No cambio para no alterar las salidas. Sin embargo en este latch se puede cometer el erro de pasar por el estado invalido, lo que podria generar un error en la salida del circuito.

La solucion al problema planteado es agregarle una linea de habilitacion al latch, de tal manera que solo trabaje cuando esta linea se encuentre activa. Este circuito se muestra en la siguiente figura.

Este circuito trabaja exactamente igual al latch S-R con una funcion adicional. Si la entrada EN es 0, la salida siempre sera No cambio. Este comportamiento describe el almacenamiento de un bit de informacion. La tabla de verdad es la siguiente:

| Entradas | Salidas | Estado | |||

| EN | ~R | ~S | Q | ~Q | |

| 1 | 0 | 0 | NC | NC | No cambio |

| 1 | 0 | 1 | 1 | 0 | Set |

| 1 | 1 | 0 | 0 | 1 | Reset |

| 1 | 1 | 1 | 0 | 0 | No valido |

| 0 | X | X | NC | NC | No cambio |

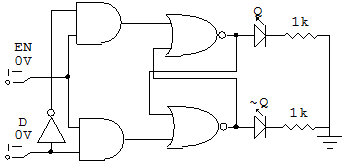

Latch D con Habilitacion

El latch S-R con habilitacion, sigue teniendo el inconveniente de presentar el estado no valido. El latch D, es una implementacion que permite eliminar este estado mejorando el comportamiento del latch. Este circuito se muestra en la siguiente figura.

Este circuito trabaja ahora solo tiene los estados de No cambio, set y reset. La tabla de verdad es la siguiente:

| Entradas | Salidas | Estado | ||

| EN | D | Q | ~Q | |

| 1 | 0 | 0 | 1 | Reset |

| 1 | 1 | 1 | 0 | Set |

| 0 | X | NC | NC | No cambio |

Emperor Casino | Shootercasino

ResponderEliminarPlay poker at the Emperor 제왕카지노 롤링 Casino! Sign-up today and claim your welcome bonus for 100% up to €1000 and 50 free spins! Play with tons of free games from the best