Los Flip-Flops son circuitos biestables sincronos. El termino sincrono indica que la salida del mismo varia unicamente en un instante de tiempo especifico de una entrada denominada reloj. Ese instante de tiempo se denomina flanco y puede haber flanco de subida y de bajada. El flanco de subida hace referencia al instante de tiempo o impulso existente cuando la entrada de reloj varia del estado 0 a 1. El flanco de bajada hace referencia al instante de tiempo o impulso existente cuando la entrada de reloj varia del estado 1 a 0. El tiempo de duracion de un flanco es de aproximadamente 30 nanosegundos.

El Flip-Flop, cambia de estado en la salida solamente cuando se presenta un flanco en su entrada de reloj. Los Flip-Flops pueden ser de flanco de subida o de flanco de bajada. Para generar un flanco es necesario implementar un circuito detector de flancos.

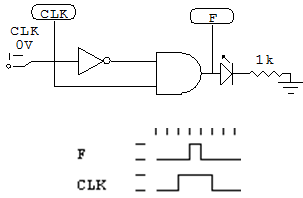

Detector de Flancos

Para implementar un circuito detector de flancos, es necesario hacer uso de una caracteristica de los circuitos TTL. Toda compuerta, tiene un tiempo de propagacion que es aproximadamente 10 ns (este tiempo puede variar segun la tecnologia de la compuerta). Con base en este concepto se puede obtener un flanco con el circuito de la siguiente figura.

Para el circuito anterior, en el instante de tiempo en que la entrada CLK, pasa de 0 a 1, la salida de la compuerta NOT se mantiene en 1 durante 10 ns, permitiendo que la salida de la compuerta AND tenga a sus entradas 1 logico durante 10 ns, dejando en la salida F un 1 logico durante 10 ns, el cual se llamara flanco de subida. En el momento en que la entrada CLK, pasa de 1 a 0, a la salida de la compuerta NOT se mantendra un 0 logico y antes de que pase a 1 logico, la otra entrada de la compuerta AND sera 0 logico, por consiguiente no hara ningun efecto al pasar de 1 a 0 la entrada CLK. Entonces de esta forma se produce un flanco de subida.

El simbolo de un circuito con reloj, puede ser con flanco de subida o flanco de bajada. En otra notacion, el reloj se puede identificar con las letras CP (Clock Pulse).

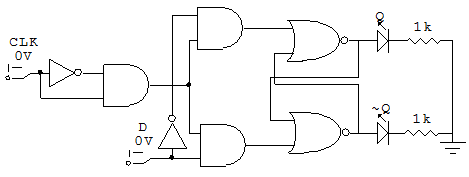

Flip-Flop D

El Flip-Flop D, es exactamente igual al latch D, reemplazando la entrada de habilitacion por un reloj. Para esto simplemente es necesario agregar al latch D, un circuito detector de flancos. La implementacion es la siguiente.

La tabla de verdad del Flip-Flop D es:

| Entradas | Salidas | Estado | ||

| CLK | D | Q | ~Q | |

| ↑ | 0 | 0 | 1 | Reset |

| ↑ | 1 | 1 | 0 | Set |

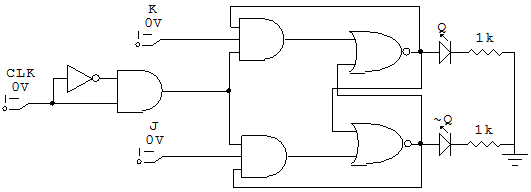

Flip-Flop J-K

El Flip-Flop J-K, es un circuito secuencial cuyo comportamiento es indentico al latch S-R en las operaciones de Set, Reset y No cambio. La ventaja del Flip-Flop J-K es que es disparado por flanco y ademas no tiene estado no valido. La implementacion es la siguiente

Este Flip-Flop tiene como caracteristica el hecho que en el estado J=1 y K=1, las salidas Q y ~Q basculan, es decir, si esta en 0 pasa a 1 y si esta en 1 pasa a 0.

La tabla de verdad del Flip-Flop J-K es:

| Entradas | Salidas | Estado | |||

| CLK | J | K | Q | ~Q | |

| ↑ | 0 | 0 | Q | ~Q | No cambio |

| ↑ | 0 | 1 | 1 | 0 | Set |

| ↑ | 1 | 0 | 0 | 1 | Reset |

| ↑ | 1 | 1 | ~Q | Q | Basculacion |

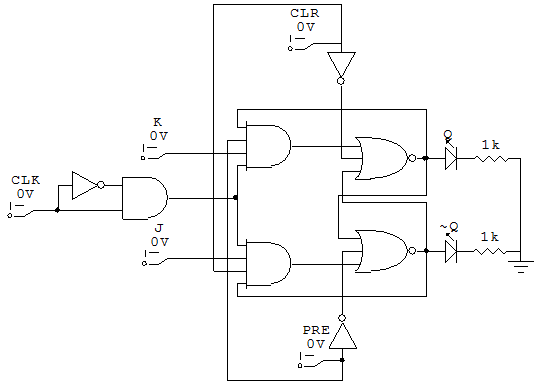

Flip-Flop J-K con entradas asincronas.

Las entradas asincronas son aquellas que no dependen de un pulso de reloj para afectar los estados de las salidas. En un Flip-Flop, puede haber dos entradas asincronas llamadas Clear y Preset. Generalmente estas entradas son activas a nivel bajo. Entonces, cuando se coloca un 0 en la entrada Clear, esta se activa y produce un 0 en la salida Q sin importar los valores de J y K. Igualmente cuando se coloca un 0 en la entrada Preset, esta se activa y produce un 1 en la salida Q sin importar los valores de J y K. La implementacion es la siguiente.

Esta de locos .....

ResponderEliminarArme el detector de flancos y lo puse a la entrada de un biestable tipo T, pero al generar el pulso, el biestable ni se inmutaba, conoces algún detector de flancos que sea funcional ?

ResponderEliminar