El temporizador 555 es un circuito bastante utilizado que puede ser configurado de dos modos distintos, como monoestable o como aestable. Un multivibrador aestable, no tiene estado estable, por consiguiente varia constantemente, es decir, este circuito oscila entre dos estados correspondientes al 0 logico (0 voltios DC) y el 1 logico (5 voltios DC).

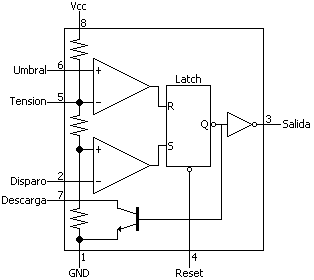

La siguiente figura muestra un diagrama con los elementos del temporizador. Los comparadores son dispositivos cuyas salidas estan a nivel alto cuando el voltaje en la entrada positiva es mayor que el voltaje en la entrada negativa y estan a nivel bajo cuando el voltaje en la entrada negativa es mayor que el voltaje en la entrada positiva. Hay un divisor de voltaje formado por tres resistencias de 5 KΩ que generan un nivel de disparo de 1/3Vcc y un novel de umbral de 2/3 de Vcc. Hay un Latch que permite almacenar el estado mientras el temporizador posee niveles bajos en las salidas de los comparadores.

Temporizador 555 configurado como aestable

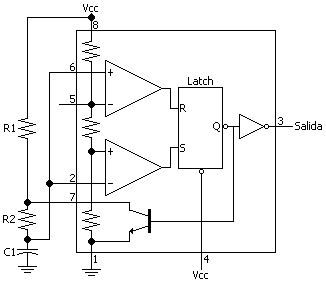

La siguiente figura muestra la configuracion de este circuito como aestable. En esta configuracion debe conectarse dos resistencias (R1 y R2) y un condensador (C1). Las entradas disparo y umbral deben conectarse a condensador C1. Los elementos R1, R2 y C1, conforman la red de temporizacion que determina la frecuencia de oscilacion.

Para comprender el funcionamiento, el temporizador cumple los siguientes eventos.

- Al conectar el circuito, el condensador C1 esta descargado, por consiguiente el voltaje en el pin 2 y 6 esta en 0V, entonces la salida del comparado B, esta a nivel alto y la salida del comparador A esta en alto. El latch hace un set. La salida ~Q esta en nivel bajo colocando el transistor en estado de corte. La salida del temporizador esta en nivel alto.

- El condensador C1 empieza a cagarse a traves de las resistencias R1 y R2. Cuando el voltaje en el condensador supera 1/3Vcc, la salida dell comparador B pasa a nivel bajo. En ese momento en el latch hay un estado de no cambio.

- El condensador C1 continua cargandose, cuando el voltaje en el condensador supera 2/3Vcc, el comparado A cambia a nivel alto. El latch hace un reset. La salida pasa a nivel bajo. El transistor queda en estado de saturacion, entonces el condensador empieza a descargarse a traves de la resistencia R2 y del transistor.

- En el momento que el condensador se descarga y su voltaje es inferior a 2/3Vcc, el comparador A pasa a nivel bajo. El latch esta en estado de no cambio.

- Cuando el condensador queda con un voltaje inferior a 1/3Vcc, el comparador B queda en nivel alto y el latch hace un set. La salida del temporizador pasa a nivel alto. El transistor queda en estado de corte. El condensador empieza a cargarse nuevamente a traves de las resistencias R1 y R2.

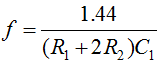

La frecuencia de oscilacion del temporizador esta dada por la siguiente formula:

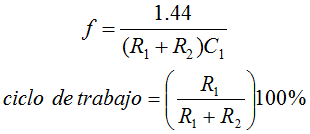

El ciclo de trabajo en este circuito, se obtiene como una relacion entre las resistencias R1 y R2, dado a que el condensador se carga a traves de R1 y R2 y se descarga a traves de R2. Entonces el ciclo de trabajo se obtiene mediante la siguiente formula:

Se puede apreciar que el ciclo de trabajo nunca sera de 50%, esto indica que el tiempo en nivel alto es diferente que el tiempo en nivel bajo.

Para obtener un ciclo de trabajo del 50%, es necesario lograr que el condensador se cargue por una resistencia y descargue por la otra. Se puede obtener colocando un diodo en paralelo a R2 con el fin que el condensador se cargue por la resistencia R1 y a traves del diodo cuya resistencia ideal es 0 y se descargue a traves de R2. Entonces con esta configuracion, la frecuencia y el ciclo de trabajo son:

Divisor de Frecuencia

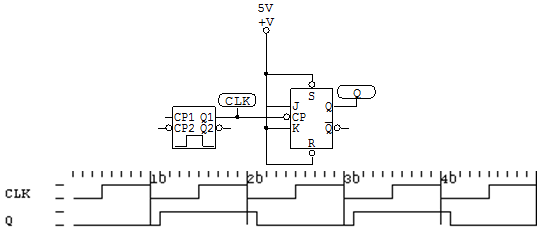

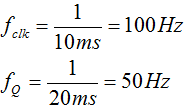

Una de las aplicaciones de los Flip-Flops es el divisor de frecuencia. El objetivo es reducir a la mitad la frecuencia de una señal periodica. Si se considera un Flip-Flop J-K y se conectan sus entradas J=K=1, la salida Q correspondera a una señal periodica con la mitad de la frecuencia de la señal original. La implementacion es la siguiente:

En el oscilograma anterior, se puede apreciar que para cada flanco de bajada del reloj, hay una basculacion que se observa en Q un instante despues dado el tiempo de propagacion del Flip-Flop. Para este ejemplo, la frecuencia del reloj equivale a:

No hay comentarios:

Publicar un comentario