Con base en el sumador completo de 4 bits, el cual se encuentra disponible en el circuito 74LS83 o 74LS283, es posible aplicar el algoritmo de la resta e implementarlo en un circuito logico. Para ello, se emplea el algoritmo de la resta que es el siguiente.

Para realizar la resta en binario se requiere seguir un algoritmo descrito por los siguientes pasos:

- Se iguala el numero de cifras en el minuendo y el sustraendo añadiendo ceros a la izquierda del numero con menos cifras.

- Se conserva el minuendo.

- Se complementa a 1 el sustraendo. El complemento consiste en la cantidad que le hace falta a un numero para alcanzar el numero maximo de su base. En el sistema binario el complemento a 1 equivale a intercambiar 1 por 0 y 0 por 1.

- Se suma el minuendo con el sustraendo complementado.

- Si existe acarreo, se suma el acarreo al resultado de la suma anterior. La existencia del acarreo indica que el resultado es positivo.

- Si no existe acarreo, se complementa a 1 el resultado de la suma anterior. La no existencia de acarreo indica que el resultado es negativo.

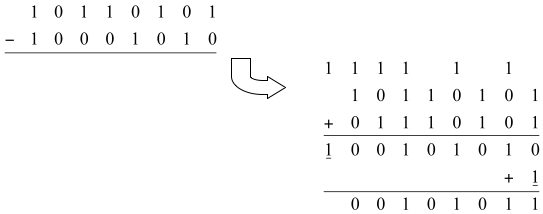

Con base en la anterior descripcion, la resta 101101012 – 100010102 es:

El resultado es 1010112 positivo

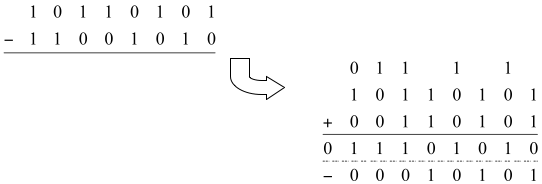

Ahora por ejemplo la resta 101101012 – 110010102 es:

El resultado es 101012 negativo

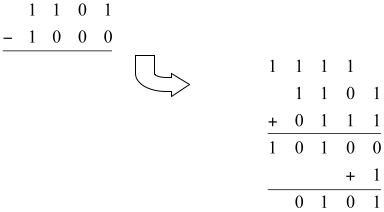

Entonces, con base en el algoritmo la resta anteriormente descrito, 11012 –10002 es:

El resultado es 01012 positivo

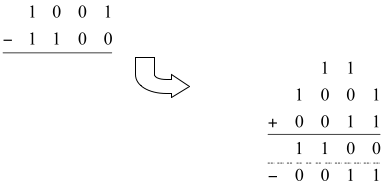

Asi mismo, con base en el algoritmo la resta anteriormente descrito, 10012 –11002 es:

El resultado es 00112 negativo

Entonces el algoritmo indica los siguientes pasos:

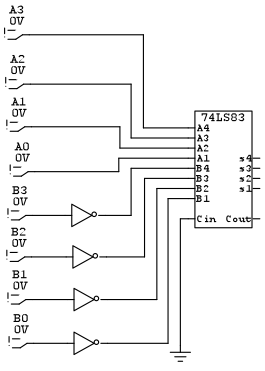

- Complementar a 1 el sustraendo. Dada dos entradas A y B, el sustraendo se puede complementar haciendo uso de la compuerta NOT.

- Sumar el minuendo con el sustraendo complementado. Se puede hacer uso entonces del CI 74283. La siguiente figura muestra estos dos pasos.

- Si el acarreo de salida es 1, entonces se suma al resultado de la suma y el resultado es positivo. Si el acarreo de salida es 0, se debe complementar el resultado de la suma y el resultado es positivo.

Entonces es debe colocar otro sumador completo, en donde la entrada A sea la salida del sumador de la figura anterior. La entrada B con el dato 00002 y el acarreo de entrada se conecta al acarreo de salida del primer sumador. Para el caso en que el acarreo de salida del primer sumador mostrado en la figura anterior, sea 1, se adicionara ese valor al resultado, si es cero se sumara 0, por consiguiente se mantiene el valor.

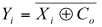

Si el acarreo es 0, se debe complementar a 1 la salida. Para ello se plantea la siguiente tabla de verdad.Co Xi Yi 0 0 1 0 1 0 1 0 0 1 1 1

En donde Co es el acarreo de salida de la primera suma. Xi es la salida de la segunda suma (esta salida esta compuesta por 4 bits) y Yi es la salida definitiva del restador (esta salida esta compuesta por 4 bits). Entonces se obtiene la siguiente expresion Booleana:

Entonces la implementacion definitiva se presenta en la siguiente figura:

puedo cambiar las compuertas por una xor?'

ResponderEliminar