Un contador es un circuito secuencial el cual cambia de estado de acuerdo una secuencia establecida por el diseño. Un contador, está construido con base de Flip-Flops. El número de Flip-Flops utilizados indica el número de bits del contador, es decir, cada Flip-Flop representa un bit dentro de la secuencia de conteo.

El termino asíncrono indica que los eventos no poseen una relación temporal fija entre ellos y que no necesariamente ocurren en el mismo instante de tiempo. Esto indica que en un contador asíncrono los Flip-Flops no comparten la misma señal de reloj.

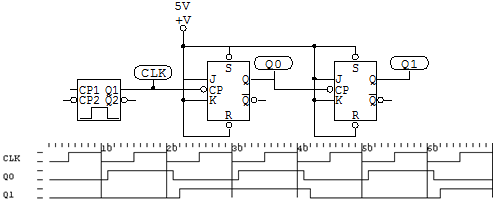

Contador Asíncrono Binario de 2 bits

Para obtener un contador asíncrono, se debe usar 2 Flip-Flops J-K flanco de bajada. Se debe conectar de la misma forma que un divisor de frecuencia. Entonces se debe conectar la señal de reloj a la entrada de reloj del primer Flip-Flop cuya salida se considera Q0. Esta salida entonces será el reloj del siguiente Flip-Flop cuya salida se denominara Q1. Las entradas J y K deben estar en 1 lógico. La siguiente figura muestra la implementación del contador y los oscilogramas que dan como resultado de su funcionamiento.

En los oscilogramas, se puede apreciar que en cada flanco de bajada del reloj, bascula Q0 y en cada flanco de bajada de Q0 bascula Q1. Analizando los valores de Q0 y Q1 en cada periodo de reloj, se nota que las salidas Q0 y Q1 forman estados que se pueden representar en una tabla denominada tabla de secuencia. El la figura anterior, se muestra que en cada basculación existe un tiempo de retardo de propagación que equivale a 30 nseg que es el tiempo de retardo de un Flip-Flop J-K.

| CLK | Q1 | Q0 |

| ↓ | 0 | 0 |

| ↓ | 0 | 1 |

| ↓ | 1 | 0 |

| ↓ | 1 | 1 |

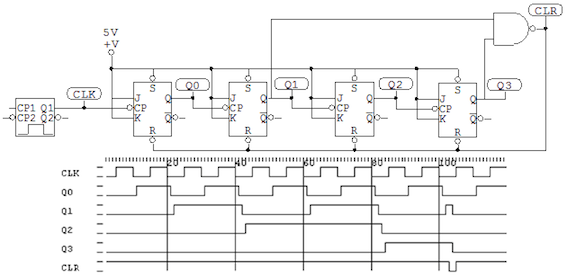

Contador Asíncrono Binario de 4 bits

Para obtener un contador asíncrono de 4 bits, se debe usar 4 Flip-Flops J-K flanco de bajada. La implementación es igual que la anterior. La siguiente figura muestra la implementación del contador y los oscilogramas que dan como resultado de su funcionamiento.

En los oscilogramas, se puede apreciar que en cada flanco de bajada del reloj, bascula Q0 y encada flanco de bajada de Q0 bascula Q1 y sucesivamente. Analizando los valores de Q0, Q1, Q2 y Q3 en cada periodo de reloj, se nota que las salidas Q0, Q1, Q2 y Q3 forman estados que se pueden representar en una tabla de secuencia.

| CLK | Q3 | Q2 | Q1 | Q0 |

| ↓ | 0 | 0 | 0 | 0 |

| ↓ | 0 | 0 | 0 | 1 |

| ↓ | 0 | 0 | 1 | 0 |

| ↓ | 0 | 0 | 1 | 1 |

| ↓ | 0 | 1 | 0 | 0 |

| ↓ | 0 | 1 | 0 | 1 |

| ↓ | 0 | 1 | 1 | 0 |

| ↓ | 0 | 1 | 1 | 1 |

| ↓ | 1 | 0 | 0 | 0 |

| ↓ | 1 | 0 | 0 | 1 |

| ↓ | 1 | 0 | 1 | 0 |

| ↓ | 1 | 0 | 1 | 1 |

| ↓ | 1 | 1 | 0 | 0 |

| ↓ | 1 | 1 | 0 | 1 |

| ↓ | 1 | 1 | 1 | 0 |

| ↓ | 1 | 1 | 1 | 1 |

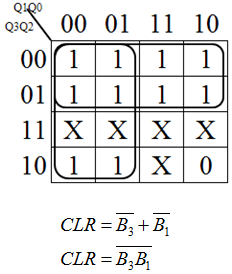

Contador Asíncrono BCD

Para obtener un contador asíncrono BCD, se debe usar 4 Flip-Flops J-K flanco de bajada. La implementación es igual que la anterior. Sin embargo requiere un elemento adicional. La cuenta debe hacerse hasta el estado 10012 lo cual indica que no se desea la presencia del estado 10102. La solución es enviar una activación del Clear cuando se presente este estado, de esta forma el estado siguiente del 10012 seria el 00002.

Para obtener estos resultados es necesario encontrar una expresión Booleana que permita obtener los resultados deseados. Para el diseño se debe partir de la tabla de secuencia del contador considerando el valor del CLR.

| Q3 | Q2 | Q1 | Q0 | CLR |

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 |

Para obtener la expresión del CLR se puede hacer un mapa de Karnaugh.

La siguiente figura muestra la implementación del contador y los oscilogramas que dan como resultado de su funcionamiento.

En los oscilogramas, se puede apreciar que en cada flanco de bajada del reloj, bascula Q0 y en cada flanco de bajada de Q0 bascula Q1 y sucesivamente. Sin embargo, en el momento es que la combinación de las salidas dan el estado 10102 hay un clear asíncrono a todos los Flip-Flops regresando rápidamente la señal de clear a nivel alto. Este pequeño impulso que se presenta en la línea de clear se denomina glitch, ya que se considera un impulso no deseado. Sin embargo, esta es la única forma de implementar contadores de modulo diferente de 2n con un contador asíncrono. En la salida Q1 también se presenta un glitch, en el instante en que el contador tiene el valor 10102.

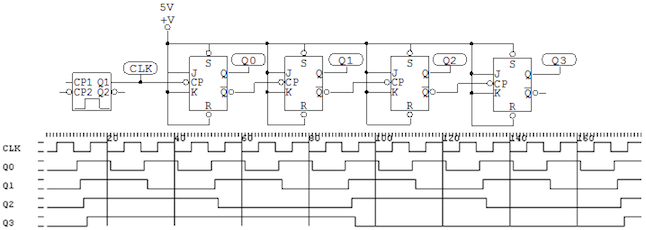

Contador Asíncrono Binario de 4 bits descendente

Para obtener un contador asíncrono de 4 bits descendente, se debe usar 4 Flip-Flops J-K flanco de subida. En este caso, la salida Q de un Flip-Flop, se convierte en el reloj del siguiente Flip-Flop. La implementación es exactamente igual al contador asíncrono binario de 4 bits, cambiando el flanco del reloj.

Otra forma de hacer la implementación, es usar Flip-Flops flanco de bajada, pero conectando la salida Q negado de un Flip-Flop al reloj del siguiente Flip-Flop. Esta segunda opción, suele ser mas conveniente debido a que en el mercado se encuentra con mayor frecuencia Flip-Flops flanco de bajada.

La siguiente figura muestra la implementación del contador y los oscilogramas que dan como resultado de su funcionamiento.

En los oscilogramas, se puede apreciar que en cada flanco de bajada del reloj, bascula Q0 y encada flanco de subida de Q0 bascula Q1 y sucesivamente. Analizando los valores de Q0, Q1, Q2 y Q3 en cada periodo de reloj, se nota que las salidas Q0, Q1, Q2 y Q3 forman estados que se pueden representar en una tabla de secuencia.

| CLK | Q3 | Q2 | Q1 | Q0 |

| ↓ | 0 | 0 | 0 | 0 |

| ↓ | 1 | 1 | 1 | 1 |

| ↓ | 1 | 1 | 1 | 0 |

| ↓ | 1 | 1 | 0 | 1 |

| ↓ | 1 | 1 | 0 | 0 |

| ↓ | 1 | 0 | 1 | 1 |

| ↓ | 1 | 0 | 1 | 0 |

| ↓ | 1 | 0 | 0 | 1 |

| ↓ | 1 | 0 | 0 | 0 |

| ↓ | 0 | 1 | 1 | 1 |

| ↓ | 0 | 1 | 1 | 0 |

| ↓ | 0 | 1 | 0 | 1 |

| ↓ | 0 | 1 | 0 | 0 |

| ↓ | 0 | 0 | 1 | 1 |

| ↓ | 0 | 0 | 1 | 0 |

| ↓ | 0 | 0 | 0 | 1 |

Contador Asíncrono Binario de 4 bits ascendente / descendente

Para obtener un contador asíncrono de 4 bits ascendente descendente, se debe usar 4 Flip-Flops J-K flanco de bajada. Para este contador, es necesario tener una entrada adicional que permita seleccionar la cuenta ascendente o descendente. Por medio de esta entrada, se desea seleccionar Q o Q negado para que se aplique al reloj del siguiente Flip-Flop. Entonces, considerando que cuando esta entrada se encuentre en 0 lógico, el contador cuente ascendente y cuando se encuentre en 1 lógico el contador cuenta descendente, se plantea el siguiente diseño.

| AD | Qn | CLK |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

La tabla anterior plantea que cuando la entrada AD sea 0, el contador cuenta ascendente y para ello se debe aplicar al reloj del siguiente Flip-Flop la línea Q. Pero cuando la entrada AD sea 1, el contador cuenta descendente y para ello se debe aplicar al reloj del siguiente Flip-Flop la línea Q negado.

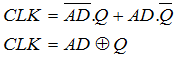

Entonces se obtiene la siguiente expresión Booleana.

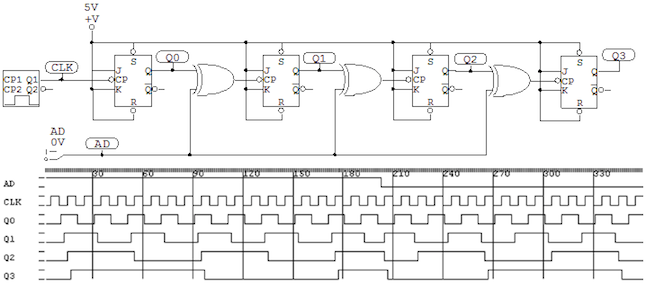

Con base en el resultado anterior, se puede concluir que al reloj del siguiente Flip-Flop, se debe aplicar una XOR entre la entrada AD y la salida Q. Esto se debe aplicar para los Flip-Flops 1, 2 y 3, debido a que el reloj del Flip-Flop 0 se encuentra conectado a la salida del temporizador.

La siguiente figura muestra la implementación del contador y los oscilogramas que dan como resultado de su funcionamiento.

En los oscilogramas, se puede apreciar que mientras la entrada AD se encuentra en 1 lógico, el contador cuenta de forma descendente. En el momento en que la entrada es 0 lógico, el contador para a contar ascendente. Analizando los valores de Q0, Q1, Q2 y Q3 en cada periodo de reloj y con base en la entrada AD, se nota que las salidas Q0, Q1, Q2 y Q3 forman estados que se pueden representar en una tabla de secuencia.

| CLK | AD | Q3 | Q2 | Q1 | Q0 |

| ↓ | 1 | 0 | 0 | 0 | 0 |

| ↓ | 1 | 1 | 1 | 1 | 1 |

| ↓ | 1 | 1 | 1 | 1 | 0 |

| ↓ | 1 | 1 | 1 | 0 | 1 |

| ↓ | 1 | 1 | 1 | 0 | 0 |

| ↓ | 1 | 1 | 0 | 1 | 1 |

| ↓ | 1 | 1 | 0 | 1 | 0 |

| ↓ | 1 | 1 | 0 | 0 | 1 |

| ↓ | 1 | 1 | 0 | 0 | 0 |

| ↓ | 1 | 0 | 1 | 1 | 1 |

| ↓ | 1 | 0 | 1 | 1 | 0 |

| ↓ | 1 | 0 | 1 | 0 | 1 |

| ↓ | 1 | 0 | 1 | 0 | 0 |

| ↓ | 1 | 0 | 0 | 1 | 1 |

| ↓ | 1 | 0 | 0 | 1 | 0 |

| ↓ | 1 | 0 | 0 | 0 | 1 |

| ↓ | 0 | 0 | 0 | 0 | 0 |

| ↓ | 0 | 0 | 0 | 0 | 1 |

| ↓ | 0 | 0 | 0 | 1 | 0 |

| ↓ | 0 | 0 | 0 | 1 | 1 |

| ↓ | 0 | 0 | 1 | 0 | 0 |

| ↓ | 0 | 0 | 1 | 0 | 1 |

| ↓ | 0 | 0 | 1 | 1 | 0 |

| ↓ | 0 | 0 | 1 | 1 | 1 |

| ↓ | 0 | 1 | 0 | 0 | 0 |

| ↓ | 0 | 1 | 0 | 0 | 1 |

| ↓ | 0 | 1 | 0 | 1 | 0 |

| ↓ | 0 | 1 | 0 | 1 | 1 |

| ↓ | 0 | 1 | 1 | 0 | 0 |

| ↓ | 0 | 1 | 1 | 0 | 1 |

| ↓ | 0 | 1 | 1 | 1 | 0 |

| ↓ | 0 | 1 | 1 | 1 | 1 |

Los asincronos no son los que no llevan reloj???

ResponderEliminarTodos los contadores tienen reloj

Eliminardisculpa tengo un problema en el que me dice diseña un contador de 0 a 15 donde solo aparezcan los numeros pares, considerando el 0 dentro de este grupo(0,2,4,6) ya tengo la tabla pero me falta hacer el mapa de karnaught pero no se como hacerlo podrias ayudarme?

EliminarLos contadores asíncronos solo conectan el flip-flop menos significativo al clock, los flip-flops mas significativos se van conectando a la salida negada de Q. Se llaman asíncronos porque no todos llevan la síncronia con el clock.

EliminarAmigo me puedes ayudar con un contador aleatorio que cuente del 1 al 6

Eliminarque tal amigo tengo una duda necesito hacer un contador de tal forma que el conteo se realice de 3 en 3 es decir 0, 3, 6, 9... no se si pudieses orientarme a como realizarlo gracias

ResponderEliminarPara hacer este conteo es necesario hacer un diseño de contador síncrono. Mediante contadores asíncronos, no lo veo posible.

Eliminary un contador ascendente descendente asincrono de 0 a 11

ResponderEliminarNecesito hacer un contador con el uso de compuertas salidas Q y Q negada y entrada CLR de 3 bits que cuente de 0 a 4 en binario y comience de nuevo. El contador inicia en 000

ResponderEliminarHola a todos,

ResponderEliminarMe pueden ayudar para realizar un circuito Contador BCD ascendente/desendente, la verdad estoy confundido y no se como aplicarlo.

Gracias

Como diseño un contador asincronico ascendente/descendente que pare en un cierto número por ejemplo 67? como le aumentaría esa condicion al diseño?

ResponderEliminary un contador que realice los factoriales del 0 al 4 en binario????

ResponderEliminar